**NEXCOM International Co., Ltd.**

# **Network and Communication Solutions Network Security Appliance NSA 5150**

User Manual

## **Contents**

#### **Preface**

| Copyright                          | i   |

|------------------------------------|-----|

| Disclaimer                         | i   |

| Acknowledgements                   | i   |

| Regulatory Compliance Statements   | i   |

| Declaration of Conformity          | i   |

| RoHS Compliance                    |     |

| Warranty and RMA                   | V   |

| Safety Information                 | vii |

| Installation Recommendations       | vii |

| Safety Precautions                 | i   |

| Technical Support and Assistance   |     |

| Conventions Used in this Manual    |     |

| Global Service Contact Information | x   |

| Package Contents                   | xii |

| Ordering Information               | xi  |

| Chapter 1: Product Introduction    |     |

| Overview                           |     |

| Key Features                       |     |

| Hardware Specifications            |     |

| Knowing Your NSA 5150              |     |

| Front Panel                        |     |

| Rear Panel                         |     |

### **Chapter 2: Jumpers and Connectors**

| Before You Begin                        |    |

|-----------------------------------------|----|

| Precautions                             | 5  |

| Jumper Settings                         | 6  |

| Locations of the Jumpers and Connectors | 7  |

| Jumpers                                 | 8  |

| RTC Clear                               | 8  |

| ATX/AT Select                           | 8  |

| Console Pin Header                      | 9  |

| WDTO Pin Header                         | 9  |

| Connector Pin Definitions               | 10 |

| External I/O Interfaces                 | 10 |

| Reset Button                            | 10 |

| RS232 Console Port                      | 10 |

| Dual USB 3.0 Ports                      | 11 |

| LAN Ports                               | 12 |

| Connector Pin Definitions               | 14 |

| Internal Connectors                     | 14 |

| Digital IO (4 Input/4 Output)           | 14 |

| COM 2 Box Header Connector (RS232)      | 14 |

| BMC COM                                 | 15 |

| USB2 Box Header                         |    |

| HW Reset Pin Header                     | 16 |

| Power Button Pin Header                 | 16 |

| NMI Pin Header                          | 17 |

| Bypass LED Pin Header                   | 17 |

| Power LED Pin Header              |    |

|-----------------------------------|----|

| HDD LED Pin Header                | 18 |

| GAL Programming Connector         | 19 |

| BMC Programming Connector         | 19 |

| BMC Reset Pin Header              | 20 |

| System Fan Connector (4-Pin)      | 20 |

| System Fan Connectors (3-Pin)     | 21 |

| Intrusion Detect Connector        | 21 |

| Internal MO-297 Connector         | 22 |

| SATA Connectors                   | 22 |

| SATA DOM Power Port               | 23 |

| Keyboard/Mouse Connector          |    |

| VGA Connector                     | 24 |

| VGA Connector                     |    |

| Parallel Interface for LCM Module |    |

| Keypad Pin Header                 | 25 |

| PSMI Connector                    | 26 |

| Power Connector                   | 26 |

| Power Connector                   | 27 |

| PCIe x4 Slot                      |    |

| LAN Module Slot                   | 29 |

|                                   |    |

| Chapter 3: System Setup           |    |

| Removing the Chassis Cover        | 33 |

| Installing a SATA DOM             | 34 |

| Installing a MO-297 SSD Module    | 37 |

| Installing a SO DIMM              | 39 |

| Installing a 3.5" SATA Hard Drive | 40 |

Installing a LAN Module ......44

## **Chapter 4: BIOS Setup**

| About BIOS Setup            | 46 |

|-----------------------------|----|

| When to Configure the BIOS  | 46 |

| Default Configuration       | 47 |

| Entering Setup              | 47 |

| Legends                     | 47 |

| BIOS Setup Utility          | 49 |

| Main                        |    |

| Advanced                    | 50 |

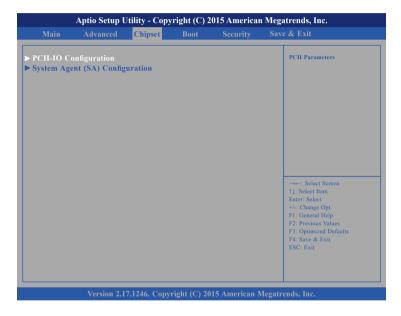

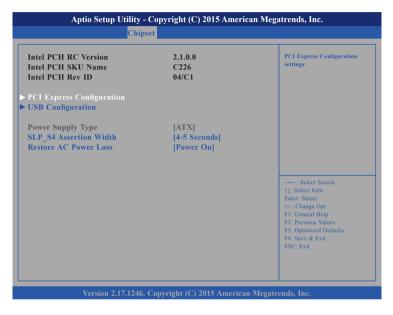

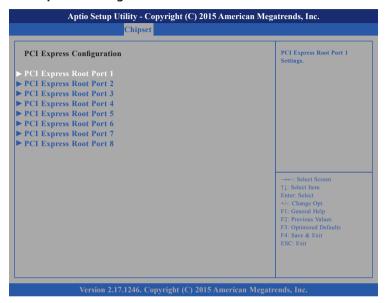

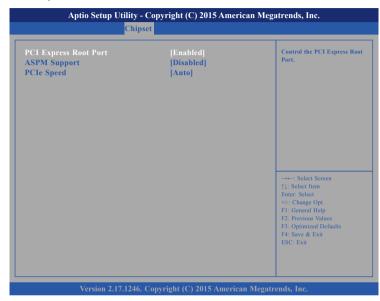

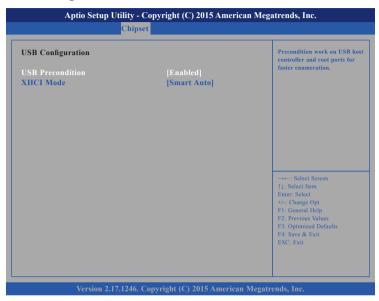

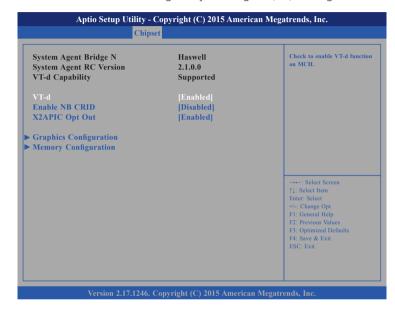

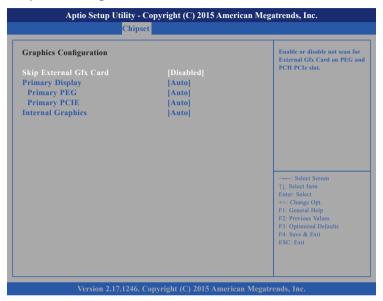

| Chipset                     | 60 |

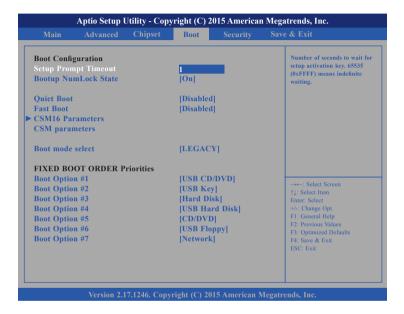

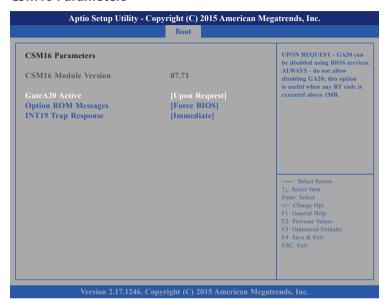

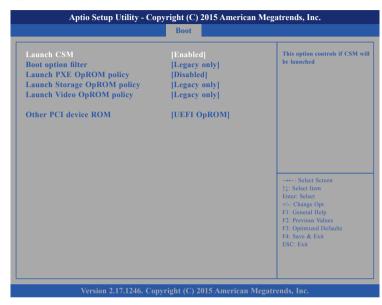

| Boot                        | 64 |

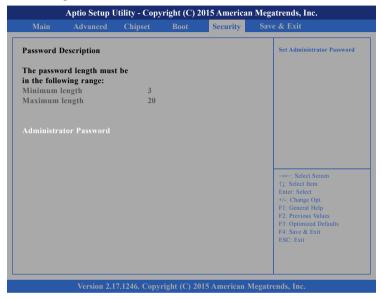

| Security                    | 66 |

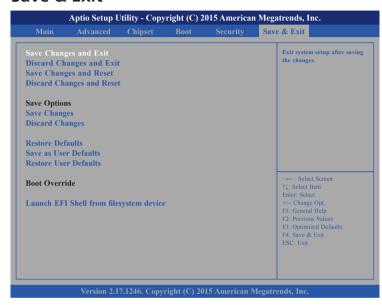

| Save & Exit                 | 66 |

| Appendix A: Bypass Register |    |

| Register Map                | 68 |

| Register Bit Definitions    | 69 |

## **Preface**

## Copyright

This publication, including all photographs, illustrations and software, is protected under international copyright laws, with all rights reserved. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written consent from NEXCOM International Co., Ltd.

### **Disclaimer**

The information in this document is subject to change without prior notice and does not represent commitment from NEXCOM International Co., Ltd. However, users may update their knowledge of any product in use by constantly checking its manual posted on our website: http://www.nexcom.com. NEXCOM shall not be liable for direct, indirect, special, incidental, or consequential damages arising out of the use of any product, nor for any infringements upon the rights of third parties, which may result from such use. Any implied warranties of merchantability or fitness for any particular purpose is also disclaimed.

## **Acknowledgements**

NSA 5150 is a trademark of NEXCOM International Co., Ltd. All other product names mentioned herein are registered trademarks of their respective owners.

## **Regulatory Compliance Statements**

This section provides the FCC compliance statement for Class B devices and describes how to keep the system CE compliant.

## **Declaration of Conformity**

#### **FCC**

This equipment has been tested and verified to comply with the limits for a Class B digital device, pursuant to Part 15 of FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. Operation of this equipment in a residential area (domestic environment) is likely to cause harmful interference, in which case the user will be required to correct the interference (take adequate measures) at their own expense.

#### CE

The product(s) described in this manual complies with all applicable European Union (CE) directives if it has a CE marking. For computer systems to remain CE compliant, only CE-compliant parts may be used. Maintaining CE compliance also requires proper cable and cabling techniques.

## **RoHS Compliance**

## **NEXCOM RoHS Environmental Policy and Status Update**

NEXCOM is a global citizen for building the digital infrastructure. We are committed to providing green products and services, which are compliant with

European Union RoHS (Restriction on Use of Hazardous Substance in Electronic Equipment) directive 2002/95/EU, to be your trusted green partner and to protect our environment.

RoHS restricts the use of Lead (Pb) < 0.1% or 1,000ppm, Mercury (Hg) < 0.1% or 1,000ppm, Cadmium (Cd) < 0.01% or 100ppm, Hexavalent Chromium (Cr6+) < 0.1% or 1,000ppm, Polybrominated biphenyls (PBB) < 0.1% or 1,000ppm, and Polybrominated diphenyl Ethers (PBDE) < 0.1% or 1,000ppm.

In order to meet the RoHS compliant directives, NEXCOM has established an engineering and manufacturing task force in to implement the introduction of green products. The task force will ensure that we follow the standard NEXCOM development procedure and that all the new RoHS components and new manufacturing processes maintain the highest industry quality levels for which NEXCOM are renowned.

The model selection criteria will be based on market demand. Vendors and suppliers will ensure that all designed components will be RoHS compliant.

#### **How to recognize NEXCOM RoHS Products?**

For existing products where there are non-RoHS and RoHS versions, the suffix "(LF)" will be added to the compliant product name.

All new product models launched after January 2006 will be RoHS compliant. They will use the usual NEXCOM naming convention.

## Warranty and RMA

#### **NEXCOM Warranty Period**

NEXCOM manufactures products that are new or equivalent to new in accordance with industry standard. NEXCOM warrants that products will be free from defect in material and workmanship for 2 years, beginning on the date of invoice by NEXCOM. HCP series products (Blade Server) which are manufactured by NEXCOM are covered by a three year warranty period.

#### **NEXCOM Return Merchandise Authorization (RMA)**

- Customers shall enclose the "NEXCOM RMA Service Form" with the returned packages.

- Customers must collect all the information about the problems encountered and note anything abnormal or, print out any on-screen messages, and describe the problems on the "NEXCOM RMA Service Form" for the RMA number apply process.

- Customers can send back the faulty products with or without accessories (manuals, cable, etc.) and any components from the card, such as CPU and RAM. If the components were suspected as part of the problems, please note clearly which components are included. Otherwise, NEXCOM is not responsible for the devices/parts.

- Customers are responsible for the safe packaging of defective products, making sure it is durable enough to be resistant against further damage and deterioration during transportation. In case of damages occurred during transportation, the repair is treated as "Out of Warranty."

- Any products returned by NEXCOM to other locations besides the customers' site will bear an extra charge and will be billed to the customer.

#### **Repair Service Charges for Out-of-Warranty Products**

NEXCOM will charge for out-of-warranty products in two categories, one is basic diagnostic fee and another is component (product) fee.

#### **Repair Service Charges for Out-of-Warranty Products**

NEXCOM will charge for out-of-warranty products in two categories, one is basic diagnostic fee and another is component (product) fee.

#### **System Level**

- Component fee: NEXCOM will only charge for main components such as SMD chip, BGA chip, etc. Passive components will be repaired for free, ex: resistor, capacitor.

- Items will be replaced with NEXCOM products if the original one cannot be repaired. Ex: motherboard, power supply, etc.

- Replace with 3rd party products if needed.

- If RMA goods can not be repaired, NEXCOM will return it to the customer without any charge.

#### **Board Level**

- Component fee: NEXCOM will only charge for main components, such as SMD chip, BGA chip, etc. Passive components will be repaired for free, ex: resistors, capacitors.

- If RMA goods can not be repaired, NEXCOM will return it to the customer without any charge.

#### Warnings

Read and adhere to all warnings, cautions, and notices in this guide and the documentation supplied with the chassis, power supply, and accessory modules. If the instructions for the chassis and power supply are inconsistent with these instructions or the instructions for accessory modules, contact the supplier to find out how you can ensure that your computer meets safety and regulatory requirements.

#### **Cautions**

Electrostatic discharge (ESD) can damage system components. Do the described procedures only at an ESD workstation. If no such station is available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a metal part of the computer chassis.

## **Safety Information**

Before installing and using the device, note the following precautions:

- Read all instructions carefully.

- Do not place the unit on an unstable surface, cart, or stand.

- Follow all warnings and cautions in this manual.

- When replacing parts, ensure that your service technician uses parts specified by the manufacturer.

- Avoid using the system near water, in direct sunlight, or near a heating device

- The load of the system unit does not solely rely for support from the rackmounts located on the sides. Firm support from the bottom is highly necessary in order to provide balance stability.

- The computer is provided with a battery-powered real-time clock circuit. There is a danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

#### **Installation Recommendations**

Ensure you have a stable, clean working environment. Dust and dirt can get into components and cause a malfunction. Use containers to keep small components separated.

Adequate lighting and proper tools can prevent you from accidentally damaging the internal components. Most of the procedures that follow require only a few simple tools, including the following:

- A Philips screwdriver

- A flat-tipped screwdriver

- A grounding strap

- An anti-static pad

Using your fingers can disconnect most of the connections. It is recommended that you do not use needle-nose pliers to disconnect connections as these can damage the soft metal or plastic parts of the connectors.

## **Safety Precautions**

- 1. Read these safety instructions carefully.

- 2. Keep this User Manual for later reference.

- 3. Disconnect this equipment from any AC outlet before cleaning. Use a damp cloth. Do not use liquid or spray detergents for cleaning.

- 4. For plug-in equipment, the power outlet socket must be located near the equipment and must be easily accessible.

- 5. Keep this equipment away from humidity.

- 6. Put this equipment on a stable surface during installation. Dropping it or letting it fall may cause damage.

- 7. The openings on the enclosure are for air convection to protect the equipment from overheating. DO NOT COVER THE OPENINGS.

- 8. Make sure the voltage of the power source is correct before connecting the equipment to the power outlet.

- 9. Place the power cord in a way so that people will not step on it. Do not place anything on top of the power cord. Use a power cord that has been approved for use with the product and that it matches the voltage and current marked on the product's electrical range label. The voltage and current rating of the cord must be greater than the voltage and current rating marked on the product.

- 10. All cautions and warnings on the equipment should be noted.

- 11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage by transient overvoltage.

- 12. Never pour any liquid into an opening. This may cause fire or electrical shock

- 13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- 14. If one of the following situations arises, get the equipment checked by service personnel:

- a. The power cord or plug is damaged.

- b. Liquid has penetrated into the equipment.

- c. The equipment has been exposed to moisture.

- d. The equipment does not work well, or you cannot get it to work according to the user's manual.

- e. The equipment has been dropped and damaged.

- f. The equipment has obvious signs of breakage.

- 15. Do not place heavy objects on the equipment.

- 16. The unit uses a three-wire ground cable which is equipped with a third pin to ground the unit and prevent electric shock. Do not defeat the purpose of this pin. If your outlet does not support this kind of plug, contact your electrician to replace your obsolete outlet.

- 17. CAUTION: DANGER OF EXPLOSION IF BATTERY IS INCORRECTLY REPLACED. REPLACE ONLY WITH THE SAME OR EQUIVALENT TYPE RECOMMENDED BY THE MANUFACTURER. DISCARD USED BATTERIES ACCORDING TO THE MANUFACTURER'S INSTRUCTIONS.

## **Technical Support and Assistance**

- For the most updated information of NEXCOM products, visit NEXCOM's website at www.nexcom.com.

- 2. For technical issues that require contacting our technical support team or sales representative, please have the following information ready before calling:

- Product name and serial number

- Detailed information of the peripheral devices

- Detailed information of the installed software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wordings of the error messages

#### Warning!

- 1. Handling the unit: carry the unit with both hands and handle it with care.

- 2. Maintenance: to keep the unit clean, use only approved cleaning products or clean with a dry cloth.

- 3. CompactFlash: Turn off the unit's power before inserting or removing a CompactFlash storage card.

#### **Conventions Used in this Manual**

#### Warning:

Information about certain situations, which if not observed, can cause personal injury. This will prevent injury to yourself when performing a task.

#### Caution:

Information to avoid damaging components or losing data.

#### Note:

Provides additional information to complete a task easily.

#### **Global Service Contact Information**

## **Headquarters NEXCOM International Co., Ltd.**

15F, No. 920, Chung-Cheng Rd., ZhongHe District, New Taipei City, 23586, Taiwan, R.O.C.

Tel: +886-2-8226-7786 Fax: +886-2-8226-7782

#### America USA NEXCOM USA

www.nexcom.com

2883 Bayview Drive, Fremont CA 94538, USA Tel: +1-510-656-2248 Fax: +1-510-656-2158 Email: sales@nexcom.com

#### Asia Taiwan NEXCOM Intelligent Systems Taipei Office

13F, No.920, Chung-Cheng Rd., ZhongHe District, New Taipei City, 23586, Taiwan, R.O.C. Tel: +886-2-8226-7796

Tel: +886-2-8226-7796 Fax: +886-2-8226-7792 Email: sales@nexcom.com.tw

www.nexcom.com.tw

## **NEXCOM Intelligent Systems Taichung Office**

16F, No.250, Sec. 2, Chongde Rd., Beitun Dist., Taichung City 406, R.O.C. Tel: +886-4-2249-1179 Fax: +886-4-2249-1172 Email: sales@nexcom.com.tw

www.nexcom.com.tw

#### Japan NEXCOM Japan

9F, Tamachi Hara Bldg., 4-11-5, Shiba Minato-ku, Tokyo, 108-0014, Japan Tel: +81-3-5419-7830 Fax: +81-3-5419-7832 Email: sales@nexcom-jp.com

#### China NEXCOM China

www.nexcom-jp.com

1F & 2F, Block A, No. 16 Yonyou Software Park, No. 68 Beiqing Road, Haidian District, Beijing, 100094, China Tel: +86-010-5704-2680

Fax: +86-010-5704-2681 Email: sales@nexcom.cn www.nexcom.cn

#### **Chengdu Office**

9F, Shuxiangxie, Xuefu Garden, No.12 Section 1, South Yihuan Rd., Chengdu, 610061, China

Tel: +86-28-8523-0186 Fax: +86-28-8523-0186 Email: sales@nexcom.cn www.nexcom.cn

#### **Shanghai Office**

Room 603/604, Huiyinmingzun Plaza Bldg., 1, No.609, Yunlin East Rd., Shanghai, 200333, China Tel: +86-21-5278-5868

Fax: +86-21-3251-6358 Email: sales@nexcom.cn

www.nexcom.cn

#### **Shenzhen Office**

Room1707, North Block, Pines Bldg., No.7 Tairan Rd., Futian Area, Shenzhen, 518040, China Tel: +86-755-8332-7203

Fax: +86-755-8332-7213 Email: sales@nexcom.cn

www.nexcom.cn

#### **Wuhan Office**

1-C1804/1805, Mingze Liwan, No. 519 South Luoshi Rd., Hongshan District, Wuhan, 430070, China

Tel: +86-27-8722-7400 Fax: +86-27-8722-7400 Email: sales@nexcom.cn

www.nexcom.cn

## Europe United Kingdom NEXCOM EUROPE

10 Vincent Avenue, Crownhill Business Centre, Milton Keynes, Buckinghamshire MK8 0AB, United Kingdom

Tel: +44-1908-267121 Fax: +44-1908-262042 Email: sales.uk@nexcom.eu

www.nexcom.eu

#### Italy NEXCOM ITALIA S.r.I

Via Gaudenzio Ferrari 29, 21047 Saronno (VA), Italia Tel: +39 02 9628 0333

Fax: +39 02 9625570

Email: nexcomitalia@nexcom.eu

www.nexcomitalia.it

## **Package Contents**

Before continuing, verify that the NSA 5150 package that you received is complete. Your package should have all the items listed in the following table.

| Item | Part Number   | Name                                              | Description                                 | Qty |

|------|---------------|---------------------------------------------------|---------------------------------------------|-----|

| 1    | 5044440031X00 | Rubber Foot Kang Yang: RF20-5-4P                  | 19.8x18x5.0mm                               | 4   |

| 2    | 6012200052X00 | PE Zipper Bag #8                                  | 170x240mm, W/China RoHS SYMBOL              | 1   |

| 3    | 6012200053X00 | PE Zipper Bag #3                                  | 100x70mm, W/China RoHS SYMBOL               | 1   |

| 4    | 6023309081X00 | Cable EDI: 232091081804-RS                        | COM Port. DB9 Female To RJ45 8P8C L:1800mm  | 1   |

| 5    | 6029900037X00 | DOW Corning 340 Silcone Heat Sink Compound(3g)    |                                             | 1   |

| 6    | 50311F0102X00 | (H)Round Head Screw Long FEI: P6#32Tx 1/4/SW7*0.8 | W/Spring+Flat Washer P6#32Tx 1/4/SW7x0.8 NI | 4   |

| 7    | 60233AT133X00 | SATA Cable ST: MD-6102042                         | SATA 7P 180D(LOCK) TO 7P 90D(LOCK) L=135mm  | 1   |

| 8    | 6014401754X00 | NSA 5150 Membrane with LCM VER: A GREATWOOD       | 42x427.8x0.582mm                            | 1   |

| 9    | 5060900301X00 | NSA 5130 Ear Sets VER: A CHYUAN-JYH               | 79.5x43.5x26mm AL Pantone 295U              | 1   |

| 10   | 50311F0148X00 | (H)Screw Long FEI: P4#40T*1/4 NIGP                | P#4-40TX6.35mm (NI)                         | 1   |

| 11   | 602DCD0757X00 | (E)NSA 5150 CD Driver VER: 1.0                    | JCL                                         | 1   |

## **Ordering Information**

The following below provides ordering information for NSA 5150.

#### Barebone

NSA 5150 (P/N: 10S00515000X0)

Support 4th generation Intel® Core™ processors, 4 DDR3 memory slots, 8PCle GbE LAN ports, MO-297 socket, USB ports, VGA port, one PCle x4 expansion slot, w/o LCM

## **Chapter 1: Product Introduction**

#### Overview

## **Key Features**

- 1U rackmount network platform

- Intel® 4th generation Core™ processors

- Support four DDR3 1333/1600 memory, up to 32GB

- Support one PCle x8 expansion

- Internal one 3.5" HDD bay/two 2.5" HDD bay (Optional)

## **Hardware Specifications**

#### **Main Board**

- NSB 5150

- Support 4th generation Intel® Core™ processors

- Intel® C226

#### **Main Memory**

4x 240-pin DDR3 1333/1600MHz DIMM sockets, up to 32GB ECC SDRAM

#### **LAN Features**

- LAN Chip: Intel® I350

- Support 10/100/1000 link speed

- LAN Bypass : 4pairs

#### **Expansion**

- 1x PCle x4 slot

- 1x LAN module

#### I/O Interface-Front

- Power status/HDD status/LAN status/Bypass status LEDs

- 2x USB 2.0 ports

- 1x RJ45 type console port

- 8x copper LAN ports

- 1x LAN Module (Optional)

#### I/O Interface-Rear

- 1x expansion slot

- 2x USB 2.0 ports

- 1x VGA port

#### **Devices**

- 1x MO-297 socket

- 1x internal 3.5" HDD bay/two 2.5" HDD Bay (Optional)

- 1x SATA-DOM device space

#### **Power Input**

250W ATX power supply/200W 1+1 redundant power supply (Optional)

#### **Chassis Dimensions**

- Chassis Dimension: 430mm x 450mm x 44mm

- Carton Dimension: 560mm x 620mm x 190mm

#### Weight

- Without packing: 8KgWith packing: 12Kg

- Certifications

- CE approval

- FCC Class A

- UL

## **Knowing Your NSA 5150**

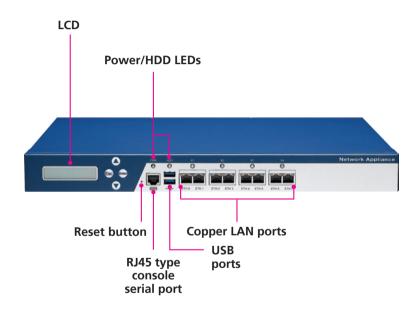

#### **Front Panel**

#### LCD

2x16 characters LCD module, PIO interface.

#### **Reset Button**

Press to restart the system.

#### Power LED

Indicates the power status of the system.

#### **HDD LED**

Indicates the status of the hard drive

#### **RJ45 Type Console Serial Port**

Used to connect RJ45 type console devices.

#### **USB Ports**

Used to connect USB 3.0/2.0 devices.

#### **Copper LAN Ports**

Used to connect LAN network devices.

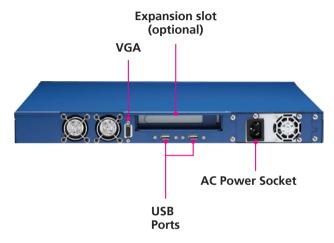

#### **Rear Panel**

#### **Expansion Slot**

Used to install a PCI Express x8 card.

#### VGA

Used to connect an analog VGA monitor.

#### **USB Ports**

Used to connect USB 2.0/1.1 devices.

#### **AC Power Socket**

Plug an AC power cord here before turning on the system.

## **Chapter 2: Jumpers and Connectors**

This chapter describes how to set the jumpers and connectors on the NSA 5150 motherboard.

## **Before You Begin**

- Ensure you have a stable, clean working environment. Dust and dirt can get into components and cause a malfunction. Use containers to keep small components separated.

- Adequate lighting and proper tools can prevent you from accidentally damaging the internal components. Most of the procedures that follow require only a few simple tools, including the following:

- A Philips screwdriver

- A flat-tipped screwdriver

- A set of jewelers screwdrivers

- A grounding strap

- An anti-static pad

- Using your fingers can disconnect most of the connections. It is recommended that you do not use needle-nosed pliers to disconnect connections as these can damage the soft metal or plastic parts of the connectors.

- Before working on internal components, make sure that the power is off.

Ground yourself before touching any internal components, by touching a metal object. Static electricity can damage many of the electronic components. Humid environments tend to have less static electricity than

dry environments. A grounding strap is warranted whenever danger of static electricity exists.

#### **Precautions**

Computer components and electronic circuit boards can be damaged by discharges of static electricity. Working on computers that are still connected to a power supply can be extremely dangerous.

Follow the guidelines below to avoid damage to your computer or yourself:

- Always disconnect the unit from the power outlet whenever you are working inside the case.

- If possible, wear a grounded wrist strap when you are working inside the computer case. Alternatively, discharge any static electricity by touching the bare metal chassis of the unit case, or the bare metal body of any other grounded appliance.

- Hold electronic circuit boards by the edges only. Do not touch the components on the board unless it is necessary to do so. Don't flex or stress the circuit board.

- Leave all components inside the static-proof packaging that they shipped with until they are ready for installation.

- Use correct screws and do not over tighten screws.

## **Jumper Settings**

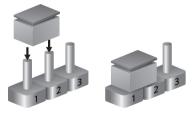

A jumper is the simplest kind of electric switch. It consists of two metal pins and a cap. When setting the jumpers, ensure that the jumper caps are placed on the correct pins. When the jumper cap is placed on both pins, the jumper is short. If you remove the jumper cap, or place the jumper cap on just one pin, the jumper is open.

Refer to the illustrations below for examples of what the 2-pin and 3-pin jumpers look like when they are short (on) and open (off).

Two-Pin Jumpers: Open (Left) and Short (Right)

Three-Pin Jumpers: Pins 1 and 2 are Short

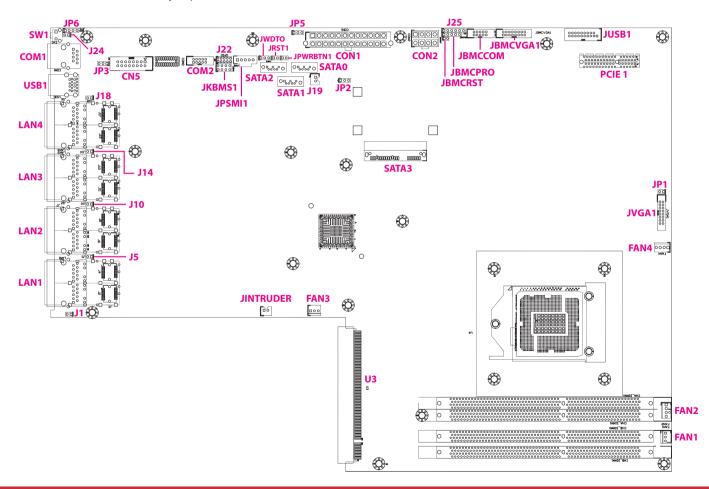

## **Locations of the Jumpers and Connectors**

The figure below shows the location of the jumpers and connectors.

## **Jumpers**

#### **RTC Clear**

Connector type: 1x3 3-pin header, 2.54mm pitch

Connector location: JP2

| Pin | Function   |

|-----|------------|

| 1-2 | Normal     |

| 2-3 | Clear CMOS |

| Pin | Definition |

|-----|------------|

| 1   | VCCRTC     |

| 2   | RTC_RST#   |

| 3   | GND        |

#### **ATX/AT Select**

Connector type: 1x3 3-pin header, 2.54mm pitch

Connector location: JP5

| Pin | Function |

|-----|----------|

| 1-2 | ATX Mode |

| 2-3 | AT Mode  |

| Pin | Definition    |

|-----|---------------|

| 1   | NC            |

| 2   | AT_ATX_SELECT |

| 3   | GND           |

#### **Console Pin Header**

Connector type: 1x3 3-pin header, 2.54mm pitch

Connector location: JP3

| Pin | Function   |

|-----|------------|

| 1-2 | RTS to CTS |

| 2-3 | Normal     |

| Pin | Description |

|-----|-------------|

| 1   | SP_RTS1_R   |

| 2   | SP_CTS1_R   |

| 3   | SP_CTS1_CON |

#### **WDTO Pin Header**

Connector type: 1x3 3-pin header, 2.54mm pitch

Connector location: JWDTO

| Pin | Function      |

|-----|---------------|

| 1-2 | NMI at WDTO   |

| 2-3 | Reset at WDTO |

| Pin | Description |  |

|-----|-------------|--|

| 1   | NMI_WDTO    |  |

| 2   | SIO_WDTO    |  |

| 3   | RST_WDTO    |  |

## **Connector Pin Definitions**

## External I/O Interfaces Reset Button

Connector location: SW1

| Pin | Definition |  |

|-----|------------|--|

| 1   | GND        |  |

| 2   | SW_BTN_IN  |  |

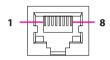

#### **RS232 Console Port**

Connector type: RJ45 port Connector location: COM1

| Pin | Definition | Pin | Definition  |

|-----|------------|-----|-------------|

| 1   | SP_RTS1_R  | 2   | SP_DTR1_R   |

| 3   | SP_TXD1_R  | 4   | GND         |

| 5   | SP_DCD1_R  | 6   | SP_RXD1_R   |

| 7   | SP_DSR1_R  | 8   | SP_CTS1_CON |

#### **Dual USB 3.0 Ports**

Connector type: Dual USB 3.0 ports

Connector location: USB1

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | 5VDUAL     | 2   | USB2-      |

| 3   | USB2+      | 4   | GND        |

| 5   | USB3_RX3-  | 6   | USB3_RX3+  |

| 7   | GND        | 8   | USB3_TX3-  |

| 9   | USB3_TX3+  | 10  | 5VDUAL     |

| 11  | USB3-      | 12  | USB3+      |

| 13  | GND        | 14  | USB3_RX4-  |

| 15  | USB3_RX4+  | 16  | GND        |

| 17  | USB3_TX4-  | 18  | USB3_TX4+  |

11

#### **LAN Ports**

Connector type: RJ45 with LEDs

Connector location: LAN1, LAN2, LAN3 and LAN4

| Act             | Status        |

|-----------------|---------------|

| Flashing Yellow | Data activity |

| Off             | No activity   |

| Link          | Status               |

|---------------|----------------------|

| Steady Green  | 1G network link      |

| Steady Yellow | 100Mbps network link |

| Off           | No link              |

#### LAN1

| Pin | Definition    | Pin | Definition   |

|-----|---------------|-----|--------------|

| A1  | PORT7_MDI0P   | A2  | PORT7_MDI0N  |

| А3  | PORT7_MDI1P   | A4  | PORT7_MDI1N  |

| A5  | LAN7_RJ_TC    | A6  | GND          |

| A7  | PORT7_MDI2P   | A8  | PORT7_MDI2N  |

| A9  | PORT7_MDI3P   | A10 | PORT7_MDI3N  |

| A11 | PORT7_L1000_N | A12 | PORT7_L100_N |

| A13 | PORT7_ACT_N   | A14 | PORT7_LINK_N |

| B1  | PORT8_MDI0P   | B2  | PORT8_MDION  |

| В3  | PORT8_MDI1P   | B4  | PORT8_MDI1N  |

| B5  | LAN8_RJ_TC    | В6  | GND          |

| В7  | PORT8_MDI2P   | B8  | PORT8_MDI2N  |

| В9  | PORT8_MDI3P   | B10 | PORT8_MDI3N  |

| B11 | PORT8_L1000_N | B12 | PORT8_L100_N |

| B13 | PORT8_ACT_N   | B14 | PORT8_LINK_N |

#### LAN2

| Pin | Definition    | Pin | Definition   |

|-----|---------------|-----|--------------|

| A1  | PORT5_MDI0P   | A2  | PORT5_MDION  |

| А3  | PORT5_MDI1P   | A4  | PORT5_MDI1N  |

| A5  | LAN5_RJ_TC    | A6  | GND          |

| A7  | PORT5_MDI2P   | A8  | PORT5_MDI2N  |

| A9  | PORT5_MDI3P   | A10 | PORT5_MDI3N  |

| A11 | PORT5_L1000_N | A12 | PORT5_L100_N |

| A13 | PORT5_ACT_N   | A14 | PORT5_LINK_N |

| B1  | PORT6_MDI0P   | B2  | PORT6_MDION  |

| В3  | PORT6_MDI1P   | B4  | PORT6_MDI1N  |

| B5  | LAN6_RJ_TC    | В6  | GND          |

| В7  | PORT6_MDI2P   | B8  | PORT6_MDI2N  |

| В9  | PORT6_MDI3P   | B10 | PORT6_MDI3N  |

| B11 | PORT6_L1000_N | B12 | PORT6_L100_N |

| B13 | PORT6_ACT_N   | B14 | PORT6_LINK_N |

#### LAN3

| Pin | Definition    | Pin | Definition   |

|-----|---------------|-----|--------------|

| A1  | PORT3_MDI0P   | A2  | PORT3_MDION  |

| A3  | PORT3_MDI1P   | A4  | PORT3_MDI1N  |

| A5  | LAN3_RJ_TC    | A6  | GND          |

| A7  | PORT3_MDI2P   | A8  | PORT3_MDI2N  |

| A9  | PORT3_MDI3P   | A10 | PORT3_MDI3N  |

| A11 | PORT3_L1000_N | A12 | PORT3_L100_N |

| A13 | PORT3_ACT_N   | A14 | PORT3_LINK_N |

| B1  | PORT4_MDI0P   | B2  | PORT4_MDION  |

| В3  | PORT4_MDI1P   | B4  | PORT4_MDI1N  |

| B5  | LAN4_RJ_TC    | В6  | GND          |

| В7  | PORT4_MDI2P   | B8  | PORT4_MDI2N  |

| В9  | PORT4_MDI3P   | B10 | PORT4_MDI3N  |

| B11 | PORT4_L1000_N | B12 | PORT4_L100_N |

| B13 | PORT4_ACT_N   | B14 | PORT4_LINK_N |

#### LAN4

| Pin | Definition    | Pin | Definition   |

|-----|---------------|-----|--------------|

| A1  | PORT1_MDI0P   | A2  | PORT1_MDION  |

| А3  | PORT1_MDI1P   | A4  | PORT1_MDI1N  |

| A5  | LAN1_RJ_TC    | A6  | GND          |

| A7  | PORT1_MDI2P   | A8  | PORT1_MDI2N  |

| A9  | PORT1_MDI3P   | A10 | PORT1_MDI3N  |

| A11 | PORT1_L1000_N | A12 | PORT1_L100_N |

| A13 | PORT1_ACT_N   | A14 | PORT1_LINK_N |

| B1  | PORT2_MDI0P   | B2  | PORT2_MDION  |

| В3  | PORT2_MDI1P   | B4  | PORT2_MDI1N  |

| B5  | LAN2_RJ_TC    | В6  | GND          |

| В7  | PORT2_MDI2P   | B8  | PORT2_MDI2N  |

| В9  | PORT2_MDI3P   | B10 | PORT2_MDI3N  |

| B11 | PORT2_L1000_N | B12 | PORT2_L100_N |

| B13 | PORT2_ACT_N   | B14 | PORT2_LINK_N |

### **Connector Pin Definitions**

## Internal Connectors Digital IO (4 Input/4 Output)

Connector type: 2x5 10-pin header, 2.0mm pitch

Connector location: J22

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | VCC5       | 2   | GND        |

| 3   | SIO_GP32   | 4   | SIO_GP06   |

| 5   | SIO_GP03   | 6   | SIO_GP07   |

| 7   | SIO_GP04   | 8   | SIO_GP76   |

| 9   | SIO_GP05   | 10  | SIO_GP77   |

#### **COM 2 Box Header Connector (RS232)**

Connector type: 2x5 10-pin header, 2.0mm pitch

Connector location: COM2

|   | Pin | Definition | Pin | Definition |

|---|-----|------------|-----|------------|

| ĺ | 1   | SP_DCD2    | 2   | SP_RXD2    |

|   | 3   | SP_TXD2    | 4   | SP_DTR2    |

|   | 5   | GND        | 6   | SP_DSR2    |

|   | 7   | SP_RTS2    | 8   | SP_CTS2    |

|   | 9   | SP_RI2     | 10  | GND        |

#### **BMC COM**

Connector type: 2x5 10-pin header, 2.0mm pitch

Connector location: JBMCCOM

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | NC         | 2   | SP_RXD     |

| 3   | SP_TXD     | 4   | NC         |

| 5   | GND        | 6   | NC         |

| 7   | NC         | 8   | NC         |

| 9   | NC         | 10  | GND        |

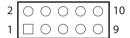

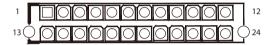

#### **USB2 Box Header**

Connector type: 2x10 20-pin header, 2.0mm pitch

Connector location: JUSB1

| 2 | 20     |

|---|--------|

| 1 | <br>19 |

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | 5VDUAL     | 2   | USB3_RX1-  |

| 3   | USB3_RX1+  | 4   | GND        |

| 5   | USB3_TX1-  | 6   | USB3_TX1+  |

| 7   | GND        | 8   | USB_0-     |

| 9   | USB_0+     | 10  | NC         |

| 11  | USB_1+     | 12  | USB_1-     |

| 13  | GND        | 14  | USB3_TX2+  |

| 15  | USB3_TX2-  | 16  | GND        |

| 17  | USB3_RX2+  | 18  | USB3_RX2-  |

| 19  | 5VDUAL     | 20  |            |

#### **HW Reset Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: JRST1

| Pin | Definition        |  |

|-----|-------------------|--|

| 1   | PCH_SYS_RESET_N_R |  |

| 2   | GND               |  |

#### **Power Button Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: JPWRBTN1

| Pin | Definition  |

|-----|-------------|

| 1   | GND         |

| 2   | FP_PWRBTN_N |

#### **NMI Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: JP1

| Pin | Definition |

|-----|------------|

| 1   | NMI_SW-    |

| 2   | GND        |

#### **Bypass LED Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: J1, J5, J10 and J14

#### J1

| Pin | Definition    |  |

|-----|---------------|--|

| 1   | VCC3          |  |

| 2   | BYPASS_LED_S4 |  |

#### J5

| Pin | Definition    |  |

|-----|---------------|--|

| 1   | VCC3          |  |

| 2   | BYPASS_LED_S3 |  |

#### J10

| Pin | Definition    |  |

|-----|---------------|--|

| 1   | VCC3          |  |

| 2   | BYPASS_LED_S2 |  |

#### J14

| Pin | Definition    |  |

|-----|---------------|--|

| 1   | VCC3          |  |

| 2   | BYPASS_LED_S1 |  |

#### **Power LED Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: J24

| Pin | Definition |

|-----|------------|

| 1   | VCC3       |

| 2   | POWER_LED  |

#### **HDD LED Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: J18

| Pin | Definition |

|-----|------------|

| 1   | VCC3       |

| 2   | HDD_LED    |

### **GAL Programming Connector**

Connector type: 1x6 6-pin header, 2.54mm pitch

Connector location: J25

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | 3VSB       | 2   | GND        |

| 3   | GAL_TCK    | 4   | GAL_TDO    |

| 5   | GAL_TDI    | 6   | GAL_TMS    |

#### **BMC Programming Connector**

Connector type: 1x5 5-pin header, 2.54mm pitch

Connector location: JBMCPRO

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | FLA_CS0    | 2   | FLA_D0     |

| 3   | FLA_D1     | 4   | FLA_D2     |

| 5   | FLA_D3     | 6   |            |

#### **BMC Reset Pin Header**

Connector type: 1x2 2-pin header, 2.54mm pitch

Connector location: JBMCRST

| Pin | Definition  |  |  |

|-----|-------------|--|--|

| 1   | BMC_RESET_N |  |  |

| 2   | GND         |  |  |

#### **System Fan Connector (4-Pin)**

Connector type: 1x4 4-pin Wafer, 2.54mm pitch

Connector location: FAN2 and FAN4

| Pin | Definition |  |  |

|-----|------------|--|--|

| 1   | GND        |  |  |

| 2   | VCC12      |  |  |

| 3   | Sense      |  |  |

| 4   | FANPWM     |  |  |

### **System Fan Connectors (3-Pin)**

Connector type: 1x3 3-pin Wafer, 2.54mm pitch

Connector location: FAN1 and FAN3

| Pin | Definition |  |  |

|-----|------------|--|--|

| 1   | GND        |  |  |

| 2   | VCC12      |  |  |

| 3   | 3 Sense    |  |  |

#### **Intrusion Detect Connector**

Connector type: 1x2 2-pin header, 2.5mm pitch

Connector location: JINTRUDER

| Pin | Definition |  |  |

|-----|------------|--|--|

| 1   | INTRUDER_N |  |  |

| 2   | GND        |  |  |

#### **Internal MO-297 Connector**

Connector type: MO-297 Connector location: SATA3

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 2   | SATA_TXP3  |

| 3   | SATA_TXN3  | 4   | GND        |

| 5   | SATA_RXN3  | 6   | SATA_RXP3  |

| 7   | GND        | 8   | NC         |

| 9   | NC         | 10  | NC         |

| 11  | GND        | 12  | GND        |

| 13  | GND        | 14  | VCC5       |

| 15  | VCC5       | 16  | VCC5       |

| 17  | GND        | 18  | NC         |

| 19  | GND        | 20  | NC         |

| 21  | NC         | 22  | NC         |

#### **SATA Connectors**

Connector type: Standard Serial ATA, 1.27mm pitch Connector location: SATA0, SATA1 and SATA2

#### SATA0

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 2   | SATA_TX0P  |

| 3   | SATA_TX0N  | 4   | GND        |

| 5   | SATA_RX0N  | 6   | SATA_RX0P  |

| 7   | GND        |     |            |

#### SATA1

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 2   | SATA_TX1P  |

| 3   | SATA_TX1N  | 4   | GND        |

| 5   | SATA_RX1N  | 6   | SATA_RX1P  |

| 7   | GND        |     |            |

#### SATA2

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 2   | SATA_TX2P  |

| 3   | SATA_TX2N  | 4   | GND        |

| 5   | SATA_RX2N  | 6   | SATA_RX2P  |

| 7   | GND        |     | _          |

# **SATA DOM Power Port**

Connector type: 1x2 2-pin header, 2.5mm pitch

Connector location: J19

| Pin | Definition |  |  |

|-----|------------|--|--|

| 1   | VCC5       |  |  |

| 2   | GND        |  |  |

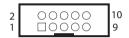

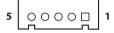

# **Keyboard/Mouse Connector**

Connector type: 2x4 8-pin header, 2.54mm pitch

Connector location: JKBMS1

| 2 | 0 | 0 | 0 | 0 | 8 |

|---|---|---|---|---|---|

| 1 |   | 0 | 0 | 0 | 7 |

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | VCC5       | 2   | VCC5       |

| 3   | KDAT       | 4   | MDAT       |

| 5   | KCLK       | 6   | MCLK       |

| 7   | GND        | 8   | GND        |

# **VGA Connector**

Connector type: 2x8 16-pin header, 2.0mm pitch

Connector location: JVGA1

0000000 16 15

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | RED_VGA    | 2   | GREEN_VGA  |

| 3   | BLUE_VGA   | 4   | NC         |

| 5   | GND        | 6   | GND        |

| 7   | CND        | 0   | CND        |

|    | Definition  |    | Deminion     |

|----|-------------|----|--------------|

| 1  | RED_VGA     | 2  | GREEN_VGA    |

| 3  | BLUE_VGA    | 4  | NC           |

| 5  | GND         | 6  | GND          |

| 7  | GND         | 8  | GND          |

| 9  | VGA_+5V     | 10 | GND          |

| 11 | NC          | 12 | DDC_DATA_VGA |

| 13 | HSYNC_VGA   | 14 | VSYNC_VGA    |

| 15 | DDC CLK VGA | 16 | NC           |

# **VGA Connector**

Connector type: 2x8 16-pin header, 2.0mm pitch

Connector location: JBMCVGA1

| 2 | <br>16 |

|---|--------|

| 1 | 15     |

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | DACROA     | 2   | DACGOA     |

| 3   | DACBOA     | 4   | NC         |

| 5   | GND        | 6   | GND        |

| 7   | GND        | 8   | GND        |

| 9   | VGA_VCC    | 10  | GND        |

| 11  | NC         | 12  | DDC_DATAO  |

| 13  | AHSYNCO    | 14  | AVSYNCO    |

| 15  | DDC_CLKO   | 16  | NC         |

24

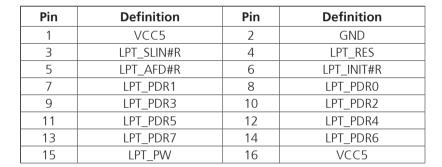

# **Parallel Interface for LCM Module**

Connector type: 2x8 16-pin header, 2.54mm pitch

Connector location: CN5

# **Keypad Pin Header**

Connector type: 1x4 4-pin header, 2.54mm pitch

Connector location: JP6

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | KEY_PIN1   | 2   | KEY_PIN2   |

| 3   | KEY_PIN3   | 4   | KEY_PIN4   |

# **PSMI Connector**

Connector type: 1x5 5-pin header, 2.54mm pitch

Connector location: JPSMI1

| Pin | Definition    | Pin | Definition |

|-----|---------------|-----|------------|

| 1   | PMBUS_CLK     | 2   | PMBUS_DATA |

| 3   | PMBUS_ALERT_N | 4   | GND        |

| 5   | NC            | 6   |            |

# **Power Connector**

Connector type: 2x12 24-pin header, 4.2mm pitch

Connector location: CON1

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | VCC3       | 2   | VCC3       |

| 3   | GND        | 4   | VCC5       |

| 5   | GND        | 6   | VCC5       |

| 7   | GND        | 8   | ATXPWROK   |

| 9   | 5VSB       | 10  | VCC12      |

| 11  | VCC12      | 12  | VCC3       |

| 13  | VCC3       | 14  | NVCC12     |

| 15  | GND        | 16  | SIO_PSON_N |

| 17  | GND        | 18  | GND        |

| 19  | GND        | 20  | GND        |

| 21  | VCC5       | 22  | VCC5       |

| 23  | VCC5       | 24  | GND        |

# **Power Connector**

Connector type: 2x4 8-pin header, 4.2mm pitch

Connector location: CON2

| Pin | Definition | Pin | Definition |

|-----|------------|-----|------------|

| 1   | GND        | 2   | GND        |

| 3   | GND        | 4   | GND        |

| 5   | VCC12_CPU  | 6   | VCC12_CPU  |

| 7   | VCC12_CPU  | 8   | VCC12_CPU  |

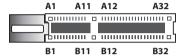

# PCIe x4 Slot

Connector type: PCle x4 Slot Connector location: PCIE1

| Pin | Definition    | Pin | Definition  |

|-----|---------------|-----|-------------|

| A1  | PRSNT1        | B1  | VCC12       |

| A2  | VCC12         | B2  | VCC12       |

| А3  | VCC12         | В3  | VCC12       |

| A4  | GND           | В4  | GND         |

| A5  | NC            | B5  | SLOT_SMC    |

| A6  | NC            | В6  | SLOT_SMD    |

| A7  | NC            | В7  | GND         |

| A8  | NC            | В8  | VCC3        |

| A9  | VCC3          | В9  | NC          |

| A10 | VCC3          | B10 | 3VSB        |

| A11 | RST_X4_SLOT_N | B11 | PCIE_WAKE_L |

| A12 | GND           | B12 | NC          |

| A13 | CK_SLOT2_DP   | B13 | GND         |

| A14 | CK_SLOT2_DN   | B14 | PCH_PE_TXP5 |

| A15 | GND           | B15 | PCH_PE_TXN5 |

| A16 | PCH_PE_RXP5   | B16 | GND         |

| Pin | Definition  | Pin | Definition  |

|-----|-------------|-----|-------------|

| A17 | PCH_PE_RXN5 | B17 | PRSNT2_1    |

| A18 | GND         | B18 | GND         |

| A19 | NC          | B19 | PCH_PE_TXP6 |

| A20 | GND         | B20 | PCH_PE_TXN6 |

| A21 | PCH_PE_RXP6 | B21 | GND         |

| A22 | PCH_PE_RXN6 | B22 | GND         |

| A23 | GND         | B23 | PCH_PE_TXP7 |

| A24 | GND         | B24 | PCH_PE_TXN7 |

| A25 | PCH_PE_RXP7 | B25 | GND         |

| A26 | PCH_PE_RXN7 | B26 | GND         |

| A27 | GND         | B27 | PCH_PE_TXP8 |

| A28 | GND         | B28 | PCH_PE_TXN8 |

| A29 | PCH_PE_RXP8 | B29 | GND         |

| A30 | PCH_PE_RXN8 | B30 | NC          |

| A31 | GND         | B31 | PRSNT2_2    |

| A32 | NC          | B32 | GND         |

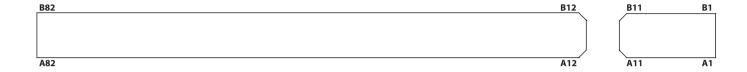

# **LAN Module Slot**

Connector location: U3

| Pin | Definition       | Pin                                    | Direction |

|-----|------------------|----------------------------------------|-----------|

| A1  | GND              | GND                                    |           |

| A2  | LPC_AD0          | LPC Multiplexed Command, Address, Data | 1/0       |

| А3  | LPC_AD1          | LPC Multiplexed Command, Address, Data | 1/0       |

| A4  | LPC_AD2          | LPC Multiplexed Command, Address, Data | 1/0       |

| A5  | LPC_AD3          | LPC Multiplexed Command, Address, Data | I/O       |

| A6  | LPC_FRAME_N      | LPC Frame                              | 0         |

| A7  | GND              | GND                                    |           |

| A8  | CK_33M_PCIE1     | 33MHz Clock output                     | 0         |

| A9  | GNG              | GND                                    |           |

| A10 | PCIE1_SLOT_RST_N | Platform Reset                         | 0         |

| A11 | GND              | GND                                    |           |

| A12 | P5V              | 5V                                     | Power     |

| A13 | P5V              | 5V                                     | Power     |

| A14 | P5V              | 5V                                     | Power     |

| A15 | P5V              | 5V                                     | Power     |

| A16 | P5V              | 5V                                     | Power     |

| A17 | P3V3             | 3.3V                                   | Power     |

| Pin  | Definition     | Pin                                     | Direction |

|------|----------------|-----------------------------------------|-----------|

| A18  | P3V3           | 3.3V                                    | Power     |

| A19  | P3V3           | 3.3V                                    | Power     |

| A20  | P3V3           | 3.3V                                    | Power     |

| A21  | P3V3           | 3.3V                                    | Power     |

| A22  | P3V3           | 3.3V                                    | Power     |

| A23  | P3V3           | 3.3V                                    | Power     |

| A24  | P12V           | 12V                                     | Power     |

| A25  | P12V           | 12V                                     | Power     |

| A26  | P12V           | 12V                                     | Power     |

| A27  | P12V           | 12V                                     | Power     |

| A28  | P12V           | 12V                                     | Power     |

| A 20 | ATV DIA/DOV D1 | Power good signal from ATX power supply | 0         |

| A29  | ATX_PWROK_B1   | 8.2K pull-high to 5VDual                |           |

| A30  | ATX_PWROK_B2   | Power good signal from ATX power supply | 0         |

|      |                | 8.2K pull-high to 5VDual                | 0         |

| A31  | GND            | GND                                     |           |

| A32  | PCIE1_SMBCLK   | SMBus Clock. 4.7K pull-high to 3.3V     | I/O       |

| Pin | Definition   | Pin                                          | Direction |

|-----|--------------|----------------------------------------------|-----------|

| A33 | PCIE1_SMBDAT | SMBus Data. 4.7K pull-high to 3.3V           | I/O       |

| A34 | GND          | GND                                          |           |

| A35 | FAN_TAC4     | Amplitude fan tachometer input               | 1         |

| A36 | GND          | GND                                          |           |

| A37 | GND          | GND                                          |           |

| A38 | GND          | GND                                          |           |

| A39 | GND          | GND                                          |           |

| A40 | GND          | GND                                          |           |

| A41 | GND          | GND                                          |           |

| A42 | GND          | GND                                          |           |

| A43 | GND          | GND                                          |           |

| A44 | GND          | GND                                          |           |

| A45 | HM VTIN1     | Temperature sensor input                     | ı         |

| A43 | HIVI_VIIIVI  | 10K pull-high to VREF                        | ı         |

| A46 | MONITOR_GND  | Temperature sensor GND                       |           |

| A47 | GND          | GND                                          |           |

| A48 | GND          | GND                                          |           |

| A49 | GND          | GND                                          |           |

| A50 | GND          | GND                                          |           |

| A51 | ALL_PWRGD    | All power OK signal                          | 0         |

| A52 | GND          | GND                                          |           |

| A53 | N12V         | NC                                           |           |

| A54 | GND          | GND                                          |           |

| A55 | GND          | GND                                          |           |

| A56 | PEGO_RX7P    | CPU Primary PCI Express Receive Differential | I         |

| A57 | PEG0_RX7N    | Pair                                         | l         |

| Pin | Definition | Pin                                          | Direction |

|-----|------------|----------------------------------------------|-----------|

| A58 | GND        | GND                                          |           |

| A59 | PEG0_TX7P  | CPU Primary PCI Express Transmit             | 0         |

| A60 | PEG0_TX7N  | Differential Pair                            | 0         |

| A61 | GND        | GND                                          |           |

| A62 | PEG0_RX6P  | CPU Primary PCI Express Receive Differential | I         |

| A63 | PEGO_RX6N  | Pair                                         | I         |

| A64 | GND        | GND                                          |           |

| A65 | PEG0_TX6P  | CPU Primary PCI Express Transmit             | 0         |

| A66 | PEG0_TX6N  | Differential Pair                            | 0         |

| A67 | GND        | GND                                          |           |

| A68 | PEGO_RX5P  | CPU Primary PCI Express Receive Differential | I         |

| A69 | PEG0_RX5N  | Pair                                         | I         |

| A70 | GND        | GND                                          |           |

| A71 | PEGO_TX5P  | CPU Primary PCI Express Transmit             | 0         |

| A72 | PEGO_TX5N  | Differential Pair                            | 0         |

| A73 | GND        | GND                                          |           |

| A74 | PEGO_RX4P  | CPU Primary PCI Express Receive Differential |           |

| A75 | PEG0_RX4N  | Pair                                         | 1         |

| A76 | GND        | GND                                          |           |

| A77 | PEG0_TX4P  | CPU Primary PCI Express Transmit             | 0         |

| A78 | PEG0_TX4N  | Differential Pair                            | 0         |

| A79 | GND        | GND                                          |           |

| A80 | GND        | GND                                          |           |

| A81 | GND        | GND                                          |           |

| A82 | GND        | GND                                          |           |

| Pin | Definition   | Pin                                                            | Direction |

|-----|--------------|----------------------------------------------------------------|-----------|

| B1  | GND          | GND                                                            |           |

| B2  | PCIE1_SEL1   | High level (3.3VSB) (Identify for module)                      | 0         |

| В3  | PCIE1_SEL2   | Low level (GND) (Identify for module)                          | 0         |

| B4  | PCIE1_SEL3   | Low level (GND) (Identify for module)                          | 0         |

| B5  | GND          | GND                                                            |           |

| В6  | GND          | GND                                                            |           |

| В7  | GND          | GND                                                            |           |

| B8  | PCIE1_SUSCLK | 32KHz Clock output                                             | 0         |

| В9  | P3V3_DUAL    | 3.3VSB                                                         | Power     |

| B10 | P3V3_DUAL    | 3.3VSB                                                         | Power     |

| B11 | P3V3_DUAL    | 3.3VSB                                                         | Power     |

| B12 | P5V          | 5V                                                             | Power     |

| B13 | P5V          | 5V                                                             | Power     |

| B14 | P5V          | 5V                                                             | Power     |

| B15 | P5V          | 5V                                                             | Power     |

| B16 | P5V          | 5V                                                             | Power     |

| B17 | P3V3         | 3.3V                                                           | Power     |

| B18 | P3V3         | 3.3V                                                           | Power     |

| B19 | P3V3         | 3.3V                                                           | Power     |

| B20 | P3V3         | 3.3V                                                           | Power     |

| B21 | P3V3         | 3.3V                                                           | Power     |

| B22 | P3V3         | 3.3V                                                           | Power     |

| B23 | P3V3         | 3.3V                                                           | Power     |

| B24 | P12V         | 12V                                                            | Power     |

| B25 | P12V         | 12V                                                            | Power     |

| B26 | P12V         | 12V                                                            | Power     |

| B27 | P12V         | 12V                                                            | Power     |

| B28 | P12V         | 12V                                                            | Power     |

| B29 | SMB_ALERT#   | SMBus ALERT#                                                   | I         |

| B30 | PE_WAKE_N    | PCI Express Device Wake Event signal<br>1K pull-high to 3VDual | I         |

| Pin   | Definition       | Pin                                           | Direction |

|-------|------------------|-----------------------------------------------|-----------|

| D 24  | ATX_PWROK_A1     | Power good signal from ATX power supply       |           |

| B31   |                  | 8.2K pull-high to 5VDual                      | Ο         |

| D.2.2 | ATV DIA/DOI/ A 2 | Power good signal from ATX power supply       | 0         |

| B32   | ATX_PWROK_A2     | 8.2K pull-high to 5VDual                      | Ο         |

| B33   | GND              | GND                                           |           |

| B34   | USB_4P           | Universal Serial Bus Port Differential signal | I/O       |

| B35   | USB_4N           | Universal Serial Bus Port Differential signal | I/O       |

| B36   | USB_OC45#        | USB device Over current Indicators            | I         |

| B37   | GND              | GND                                           |           |

| B38   | GND              | GND                                           |           |

| B39   | GND              | GND                                           |           |

| B40   | GND              | GND                                           |           |

| B41   | GND              | GND                                           |           |

| B42   | GND              | GND                                           |           |

| B43   | GND              | GND                                           |           |

| B44   | GND              | GND                                           |           |

| B45   | GND              | GND                                           |           |

| B46   | GND              | GND                                           |           |

| B47   | GND              | GND                                           |           |

| B48   | GND              | GND                                           |           |

| B49   | GND              | GND                                           |           |

| B50   | GND              | GND                                           |           |

| B51   | GND              | GND                                           |           |

| B52   | GND              | GND                                           |           |

| B53   | GND              | GND                                           |           |

| B54   | GND              | GND                                           |           |

| B55   | GND              | GND                                           |           |

| B56   | PEG0_RX3P        | CPU Primary PCI Express Receive Differential  | I         |

| B57   | PEGO_RX3N        | Pair                                          | I         |

| B58   | GND              | GND                                           |           |

| Pin | Definition  | Pin                                          | Direction |

|-----|-------------|----------------------------------------------|-----------|

| B59 | PEG0_TX3P   | CPU Primary PCI Express Transmit             | 0         |

| B60 | PEG0_TX3N   | Differential Pair                            | 0         |

| B61 | GND         | GND                                          |           |

| B62 | PEG0_RX2P   | CPU Primary PCI Express Receive Differential | I         |

| B63 | PEG0_RX2N   | Pair                                         | I         |

| B64 | GND         | GND                                          |           |

| B65 | PEG0_TX2P   | CPU Primary PCI Express Transmit             | 0         |

| B66 | PEG0_TX2N   | Differential Pair                            | 0         |

| B67 | GND         | GND                                          |           |

| B68 | PEGO_RX1P   | CPU Primary PCI Express Receive Differential | I         |

| B69 | PEG0_RX1N   | Pair                                         | I         |

| B70 | GND         | GND                                          |           |

| B71 | PEG0_TX1P   | CPU Primary PCI Express Transmit             | 0         |

| B72 | PEG0_TX1N   | Differential Pair                            | 0         |

| B73 | GND         | GND                                          |           |

| B74 | PEG0_RX0P   | CPU Primary PCI Express Receive Differential | I         |

| B75 | PEGO_RX0N   | Pair                                         | I         |

| B76 | GND         | GND                                          |           |

| B77 | PEG0_TX0P   | CPU Primary PCI Express Transmit             | 0         |

| B78 | PEG0_TX0N   | Differential Pair                            | 0         |

| B79 | GND         | GND                                          |           |

| B80 | CK_SLOT1_DP | Differential PCI Express Clock               | 0         |

| B81 | CK_SLOT1_DN | Differential PCI Express Clock               | 0         |

| B82 | GND         | GND                                          |           |

# **Chapter 3: System Setup**

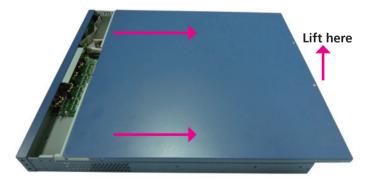

# **Removing the Chassis Cover**

Prior to removing the chassis cover, make sure the unit's power is off and disconnected from the power sources to prevent electric shock or system damage.

1. Remove the screws on the chassis cover then put them in a safe place for later use.

$\ensuremath{\mathsf{2}}.$  Gently slide the cover outwards, then lift up the cover to remove it.

# **Installing a SATA DOM**

1. Locate the SATA DOM connector on the board.

2. Fasten a copper post on the mounting hole.

3. Install the SATA DOM to the connector with the mounting hole aligned to the copper post.

4. Fasten a screw on top of the copper post.

5. Connect the power cable to the power connector on the board.

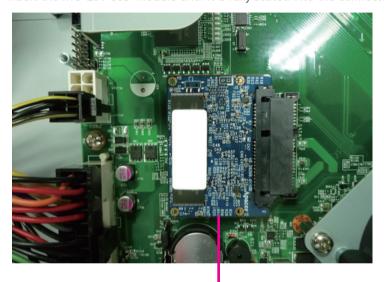

# **Installing a MO-297 SSD Module**

1. Locate the MO-297 connector on the board.

MO-297 connector

2. Insert the MO-297 SSD module until it is fully seated into the connector.

MO-297 module

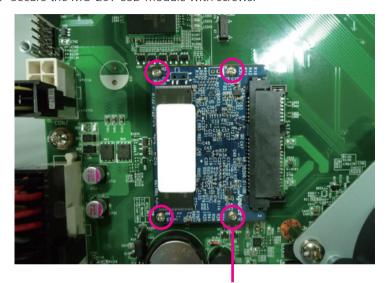

3. Secure the MO-297 SSD module with screws.

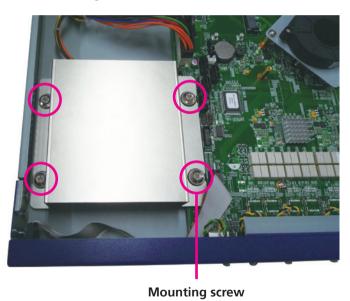

**Mounting screw**

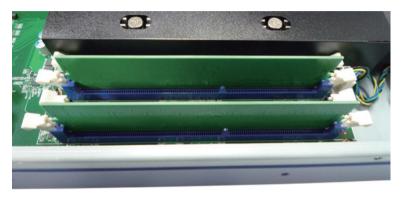

# **Installing a SO DIMM**

1. Locate the SO DIMM sockets on the board.

2. Release the locks on the SO DIMM sockets.

3. Insert the module into the socket at an 90 degree angle. Apply firm even pressure to each end of the module until it slips into the socket.

4. While pushing the SO DIMM into the position, the lock will close automatically.

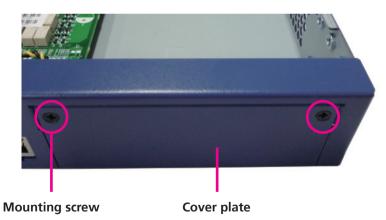

# **Installing a 3.5" SATA Hard Drive**

Please correctly follow the below instructions and noted items to avoid making unnecessary damages.

1. Remove the mounting screws that secure the hard drive bracket to the chassis.

2. Note the sides of the hard drive bracket. The longer side is designed to fit on the chassis' standoff while the shorter side is designed to fit on the motherboard's standoff

3. Place the SATA hard drive into the hard drive bracket with the SATA connector facing outwards.

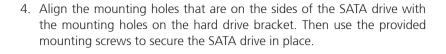

SATA data and power connector

5. Repeat step 4 for securing the screws on the other side of the hard drive bracket.

41

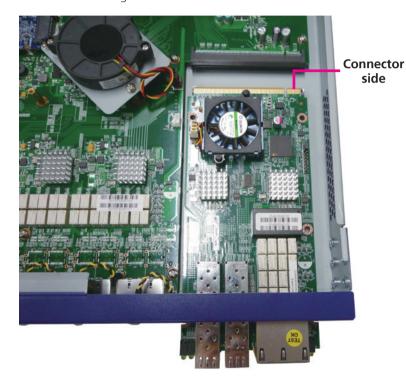

6. Place the drive into the chassis with the connector side facing the board, and then use the provided mounting screws to secure the hard drive bracket in place.

Connector side

7. Locate the SATA data connector on the board.

**SATA** data connector

8. Plug the SATA data cable onto the connector, then plug the other end to the SATA data connector on the hard drive.

**SATA** data cable

**SATA** data connector

9. Plug the SATA power cable to the SATA power connector on the hard drive.

**SATA** power cable

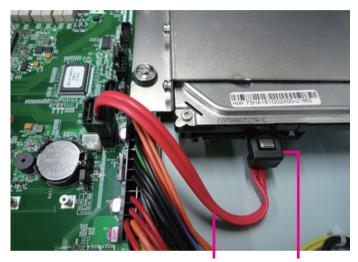

# **Installing a LAN Module**

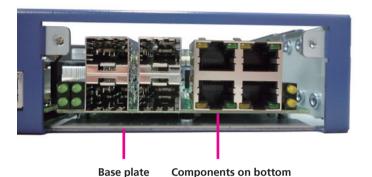

The system is equipped with 1 LAN module bay. To install a LAN module, please follow the instructions below.

Please correctly follow the below instructions and noted items to avoid making unnecessary damages. Make sure the power supply is switched off and disconnected from the power sources before replacing or adding LAN modules to prevent electric shock or system damage.

1. Remove the screw on the cover plate of the LAN module then put them in a safe place for later use.

2. Place the LAN module into the tray making sure the connector side of the module is facing inwards.

The components on the bottom of the LAN module is mounted very close to the base plate of the chassis, you may damage the components if excessive force is used. When installing or removing, please handle the LAN module with care.

3. Once the module is plugged into the LAN module connector, use the provided screws to secure the module in place. Then replace the cover plate and the chassis cover to complete.

## Important:

Before using Optical fiber for transferring data, make sure you have connected an approved Optical Transceiver Module. User needs to install appropriate and UL approved Laser Class I Transceivers, rated 3.3Vdc, max. 1W.

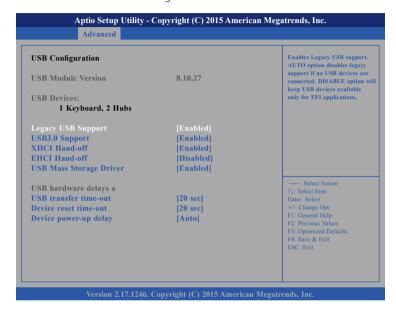

# **Chapter 4: BIOS Setup**

This chapter describes how to use the BIOS setup program for the NSA 5150. The BIOS screens provided in this chapter are for reference only and may change if the BIOS is updated in the future.

To check for the latest updates and revisions, visit the NEXCOM Web site at www.nexcom.com.tw

# **About BIOS Setup**

The BIOS (Basic Input and Output System) Setup program is a menu driven utility that enables you to make changes to the system configuration and tailor your system to suit your individual work needs. It is a ROM-based configuration utility that displays the system's configuration status and provides you with a tool to set system parameters.

These parameters are stored in non-volatile battery-backed-up CMOS RAM that saves this information even when the power is turned off. When the system is turned back on, the system is configured with the values found in CMOS.

With easy-to-use pull down menus, you can configure such items as:

- Hard drives, diskette drives, and peripherals

- Video display type and display options

- Password protection from unauthorized use

- Power management features

The settings made in the setup program affect how the computer performs. It is important, therefore, first to try to understand all the setup options, and second, to make settings appropriate for the way you use the computer.

# When to Configure the BIOS

- This program should be executed under the following conditions:

- When changing the system configuration

- When a configuration error is detected by the system and you are prompted to make changes to the setup program

- When resetting the system clock

- When redefining the communication ports to prevent any conflicts

- When making changes to the Power Management configuration

- When changing the password or making other changes to the security setup

Normally, CMOS setup is needed when the system hardware is not consistent with the information contained in the CMOS RAM, whenever the CMOS RAM has lost power, or the system features need to be changed.

# **Default Configuration**

Most of the configuration settings are either predefined according to the Load Optimal Defaults settings which are stored in the BIOS or are automatically detected and configured without requiring any actions. There are a few settings that you may need to change depending on your system configuration.

# **Entering Setup**

When the system is powered on, the BIOS will enter the Power-On Self Test (POST) routines. These routines perform various diagnostic checks; if an error is encountered, the error will be reported in one of two different ways:

- If the error occurs before the display device is initialized, a series of beeps will be transmitted

- If the error occurs after the display device is initialized, the screen will display the error message.

Powering on the computer and immediately pressing lows you to enter Setup.

# Legends

| Key                                         | Function                                                                 |

|---------------------------------------------|--------------------------------------------------------------------------|

| ← →                                         | Moves the highlight left or right to select a menu.                      |

| <b>†</b>                                    | Moves the highlight up or down between sub-menu or fields.               |

| Esc                                         | Exits the BIOS Setup Utility.                                            |

| +                                           | Scrolls forward through the values or options of the highlighted field.  |

| -                                           | Scrolls backward through the values or options of the highlighted field. |

| Tab<br>•••••••••••••••••••••••••••••••••••• | Selects a field.                                                         |

| F1                                          | Displays General Help.                                                   |

| F2                                          | Load previous values.                                                    |

| F3                                          | Load optimized default values.                                           |

| F4                                          | Saves and exits the Setup program.                                       |

| Enter,                                      | Press <enter> to enter the highlighted sub-menu</enter>                  |

## Scroll Bar

When a scroll bar appears to the right of the setup screen, it indicates that there are more available fields not shown on the screen. Use the up and down arrow keys to scroll through all the available fields.

## Submenu

When " $\blacktriangleright$ " appears on the left of a particular field, it indicates that a submenu which contains additional options are available for that field. To display the submenu, move the highlight to that field and press  $\blacksquare$ .

# **BIOS Setup Utility**

Once you enter the AMI BIOS Setup Utility, the Main Menu will appear on the screen. The main menu allows you to select from several setup functions and one exit. Use arrow keys to select among the items and press to accept or enter the submenu.

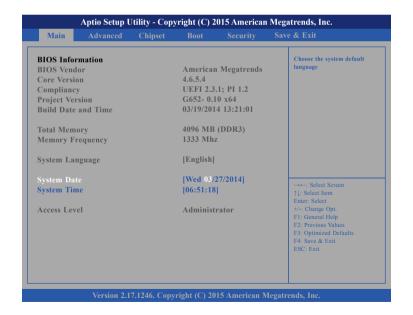

## Main

The Main menu is the first screen that you will see when you enter the BIOS Setup Utility.

#### **System Date**

The date format is <day>, <month>, <date>, <year>. Day displays a day, from Monday to Sunday. Month displays the month, from January to December. Date displays the date, from 1 to 31. Year displays the year, from 1999 to 2099.

## **System Time**

The time format is <hour>, <minute>, <second>. The time is based on the 24-hour military-time clock. For example, 1 p.m. is 13:00:00. Hour displays hours from 00 to 23. Minute displays minutes from 00 to 59. Second displays seconds from 00 to 59.

#### **Access Level**

Displays the access level of the current user in the BIOS.

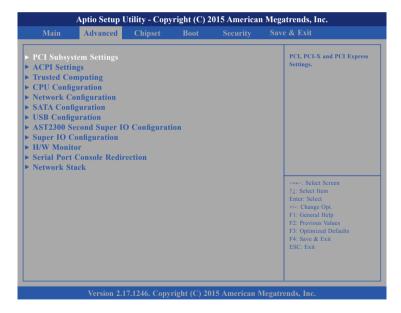

# **Advanced**

The Advanced menu allows you to configure your system for basic operation. Some entries are defaults required by the system board, while others, if enabled, will improve the performance of your system or let you set some features according to your preference.

Setting incorrect field values may cause the system to malfunction.

50

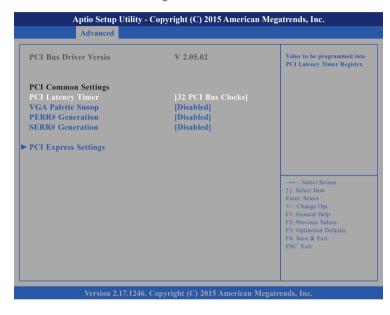

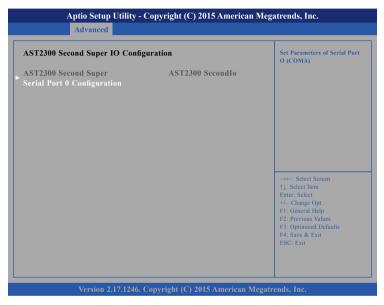

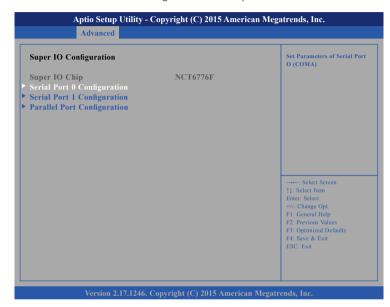

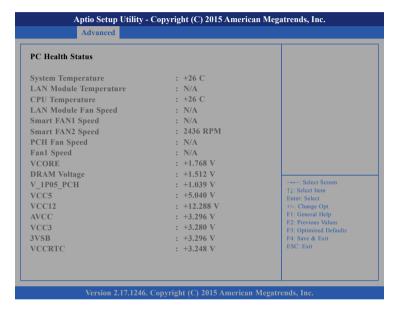

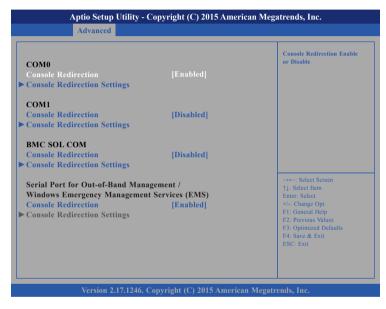

# **PCI Subsystem Settings**

This section is used to configure the PCI.

## **PCI Latency Timer**

This feature is used to select the length of time each PCI device will control the bus before another takes over. The larger the value, the longer the PCI device can retain control of the bus. Since each access to the bus comes with an initial delay before any transaction can be made, low values for the PCI Latency Timer will reduce the effectiveness of the PCI bandwidth while higher values will improve it.

# **VGA Palette Snoop**

Enables or disables the VGA palette registers snooping.

#### PERR# Generation

Enables or disables the PCI device to generate PERR#.

#### **SFRR#** Generation

Enables or disables the PCI device to generate SERR#.

# **ACPI Settings**

This section is used to configure ACPI settings.

## **Enable ACPI Auto Conf**

Enables or disables BIOS ACPI auto configuration.

## **Lock Legacy Resources**

Enables or disables lock of legacy resources

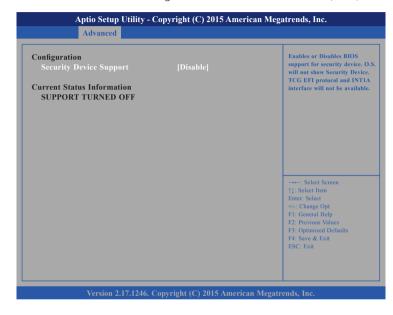

# **Trusted Computing**

This section is used to configure Trusted Platform Module (TPM) settings.

## **Security Device Support**

Enables or disables BIOS support for security device. O.S will not show Security Device. TCG EFI protocol and INT1A interface will not be available.

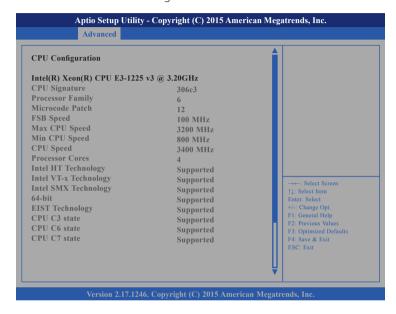

# **CPU Configuration**

This section is used to configure the CPU.

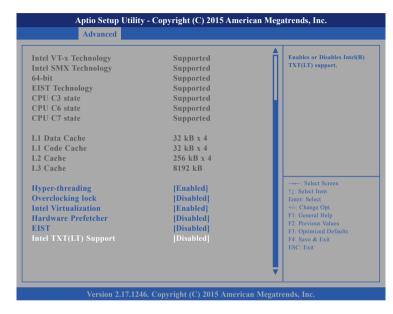

## **Hyper-Threading**

Enable this field for Windows XP and Linux which are optimized for Hyper-Threading technology. Select disabled for other OSes not optimized for Hyper-Threading technology. When disabled, only one thread per enabled core is enabled.

# **Overclocking Lock**

Enables or disables overclocking lock.

#### Intel® Virtualization

When this field is set to Enabled, the VMM can utilize the additional hardware capabilities provided by Vanderpool Technology.

#### Hardware Prefetcher

Turns on or off the MLC streamer prefetcher

#### **EIST**

Enables or disables Intel® SpeedStep.

#### Intel TXT(LT) Support

Enables or disables Intel TXT(LT).

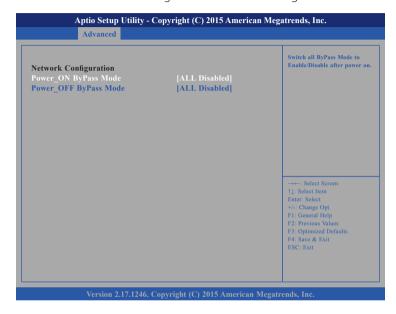

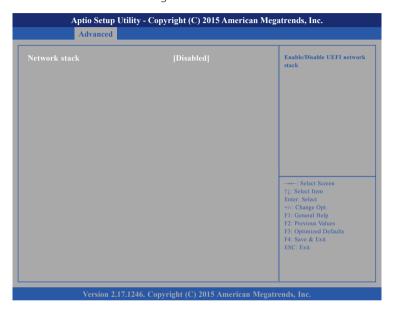

# **Network Configuration**

This section is used to configure the network settings.

## Power\_ON ByPass Mode

Enables or disables the LAN module bypass mode after the system powers on.

#### Power\_OFF ByPass Mode

Enables or disables the LAN module bypass mode after the system powers off.

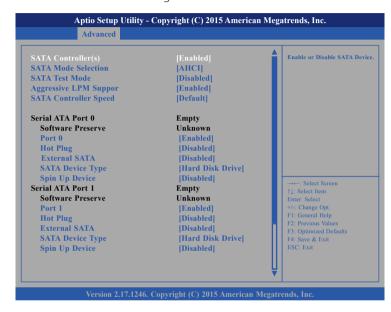

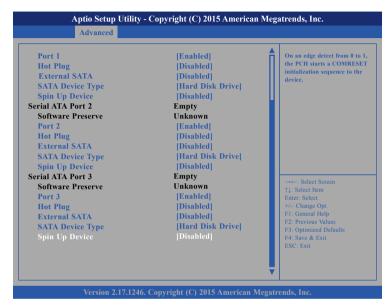

# **SATA Configuration**

This section is used to configure the SATA drives.

## SATA Controller(s)

AHCI

Enables or disables the SATA controller.

## **SATA Mode Selection**

Configures the SATA as IDE, AHCI or RAID mode.

This option configures the Serial ATA drives as Parallel ATA physical storage device.

This option configures the Serial ATA drives to use AHCI (Advanced Host Controller Interface). AHCI allows the storage driver to enable the advanced Serial ATA features which will increase storage performance.

#### **SATA Test Mode**

Enables or disables SATA test mode.

# **Aggressive LPM Support**

Enables or disables agressive LPM support.

## **SATA Controller Speed**

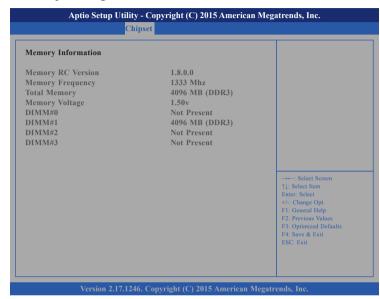

Configures the SATA controller as Gen1, Gen2 or Gen3.